## M.Sc. 1st Semester Examination, 2019 **ELECTRONICS**

(Analog Economics)

PAPER -ELC-104

Full Marks: 50

Time: 2 hours

The figures in the right-hand margin indicate marks

Candidates are required to give their answers in their own words as far as practicable

Illustrate the answers wherever necessary

## 1. Answer any four questions:

$2 \times 4$

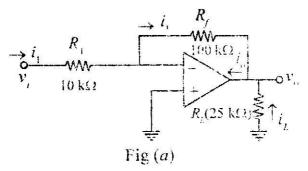

(a) In Fig(a) below, given that  $R_1 = 10 \text{ k}\Omega$ ,  $R_f = 100 \text{ k}\Omega$ ,  $V_i = 1 \text{ V}$ . A load of 25 k $\Omega$  is connected to the output terminal. Calculate (i)  $i_1$  (ii)  $v_0$  (iii)  $i_L$  and total current  $i_0$  into the output pin.

2

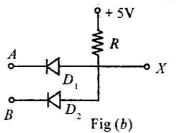

(b) Fig (b) shows a diode logic circuit. Write its truth table and mention its logic operation.

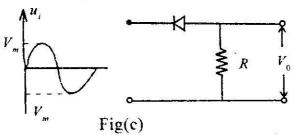

(c) What will be the output of the following circuit in Fig(c)?

- (d) Write two advantages of Switch mode power supply (SMPS) over linear power supply.

- (e) What is the importance of stabilization of Q point? 2

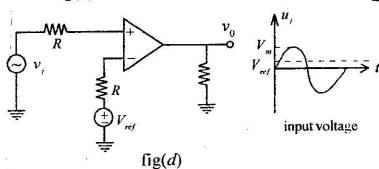

- (f) What will be the output of the following fig(d)?

2

- (g) How a PLL can be used as an FM demodulator? Write its advantages over conventional FM discriminators. 1+1

- (h) Implement  $y = \overline{AB + C}$  by using CMOS. 2

- 2. Answer any four questions:  $4 \times 4$

- (a) By proper circuit diagram explain square

wave generator circuit and derive the expression for its output frequency.

- (b) Explain series regulator circuit using op-amp. 4

- (c) How does a MOSFET work as an amplifier circuit? Explain it using proper VTC curve. 4

- (d) Which method gives best stability? Explain it using proper circuit diagram. 1+3

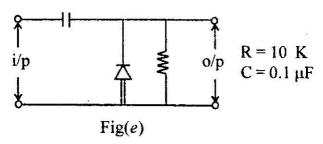

- (e) Explain clamper circuit given below. Show the O/P waveform.

- (f) Explain principle operation of VCO by proper circuit diagram.

- (g) Draw different topologies of feedback amplifier circuit.

4

4

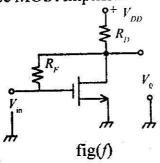

(h) Derive the expression for the small signal voltage gain of the following common source MOS Amplifier.

3. Answer any two questions:

$8 \times 2$

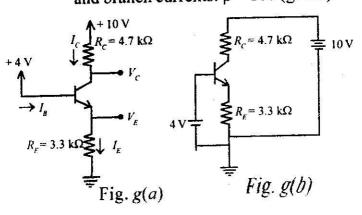

(a) (i) Consider the circuit shown in Fig g(a) which is redrawn in Fig. g(b). Analyze the circuit to determine all node voltages and branch currents.  $\beta = 100$  (given)

- (ii) Write down thermal Runway of a BJT. 6+2

- (b) (i) Draw small signal model of a MOSFET.

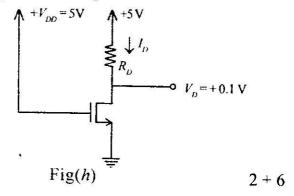

- (ii) Design the circuit shown in Fig(h) to establish a drain voltage of 0.1 V. What is the effective resistance between drain and source at the operating point? Let  $v_{th} = 1 \text{ V}$  and  $K'_{p}(W/L) = 1 \text{ mA}|V^{2}$ .

- (c) (i) Draw the circuit diagram of an emitter coupled differential amplifier and derive the expression for its CMRR.

- (ii) Explain how a current mirror circuit is designed using low  $\beta$  transistors in the

design of an op-amp with proper circuit diagram and necessary derivation. (1+3)+(1+3)

- (d) (i) With suitable circuit diagram, explain the operation of R-C coupled transistor amplifier. Mention function of all its components.

- (ii) Explain the principle of operation of Darlington amplifier. 5+3

[ Internal Assessment: 10 Marks]

1